# **DIPLOMARBEIT**

# FPGA-BASIERTES RISC-V-COMPUTERSYSTEM: YARM

| Abteil                                                                                 | ung                                                                 |  |  |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| ELEKTRONIK UND TECHNISCHE INFORMATIK                                                   |                                                                     |  |  |  |

| Ausgeführt im Schuljahr 2019/20 von:                                                   | Betreuer/Betreuerin:                                                |  |  |  |

| Armin Brauns 5AHEL<br>Daniel Plank 5BHEL                                               | DiplIng. Christoph Schönherr                                        |  |  |  |

| Projektpartner: IT-Syndikat, Verein zur F<br>scher Fort- und Weiterbildung jeglicher A | örderung des freien Zugangs zu techni<br>Art, Hackerspace Innsbruck |  |  |  |

| Ansprechpartner: Ing. David Oberhollen                                                 | zer B.Sc.                                                           |  |  |  |

| Innsbruck, am 27. März 2020                                                            |                                                                     |  |  |  |

| Abgabevermerk:<br>Datum:                                                               | Betreuer/in:                                                        |  |  |  |

### Gendererklärung

Aus Gründen der besseren Lesbarkeit wird in dieser Diplomarbeit die Sprachform des generischen Maskulinums angewendet. Es wird an dieser Stelle darauf hingewiesen, dass die ausschließliche Verwendung der männlichen Form geschlechtsunabhängig verstanden werden soll.

This thesis is written in the language form if the generic masculin for improved readability. It is pointed out that all masculin-only uses may and should be interpreted as gender neutral.

### Kurzfassung/Abstract

Diese Diplomarbeit beschäftigt sich mit der Arbeitsweise von Prozessoren und Prozessorperipherie in moderner und traditioneller Form. Sie versucht anschaulich den Aufbau eines Computersystems in Hard- und Software veranschaulichen sowie diesen erklären. Dafür wurde auf einem XILINX FPGA ein RISC-V32I Prozessor in VHDL implementiert sowie diverse Parallelbus gebundene Hardwareperipherie entwickelt und gebaut. Als Harwareperipherie wurde ein 8-Bit 2-Kanal DAC und eine serielle Schnittstelle mit TIA-/EIA-232 Pegeln gebaut. Der Prozessor implementiert das RISC-V32I base instruction set. Aufgrund der starken Verwendung von Englisch im Software- und Hardwarebereich wurde diese Diplomarbeit in Englisch verfasst, was ebenfalls die Lesbarkeit erhöhen soll. Die entstandene Dokumentation soll für Menschen mit einem Grundlegenden Verständnis von Elektronik sowie der Hardware-Beschreibungssprache VHDL verständlich sein.

This diploma thesis deals with the operation of processors and their orresponding peripherials in modern andd traditional forms. It attempts to illustrate the structure of a computersystem in hard- and software. To reach this goal a RISC-V32I processor has been implemented in VHDL on a XILINX FPGA as well as some peripherials bound to the parallel bus. These peripherials include a 2-channel 8-bit Digital to analog converter as well as a TIA-/EIA-232 compliant serial interface. Due to the common use of english in the hardware and software engineering field this thesis was written in english, which should enhance readability as well. The written documentation should be understandable for everyone with a basic understanding of electronics as well as the hardware description language VHDL.

### Result

The project was fully implemented with all functionality originally targeted. The system has been tested and verified and all example code have been documented and tested as running. Implementations in hardware were made in open-source programs and the RISC-V processor can compile using an open source toolchain. The completed project can be found on the USB stick which accompanies this thesis, or in the git repositories at https://git.it-syndikat.org/tyrolyean/dipl.git and https://gitlab.com/YARM-project/.

## **Contents**

| G                       | Gendererklärungi     |                |                              |          |  |  |

|-------------------------|----------------------|----------------|------------------------------|----------|--|--|

| Kı                      | Kurzfassung/Abstract |                |                              |          |  |  |

| R                       | Resultii             |                |                              |          |  |  |

| 1                       | Tas                  | k descri       | ption                        | 1        |  |  |

|                         | 1.1                  | Hardwa         | ıre                          | 1        |  |  |

| 2 Hardware peripherials |                      |                |                              |          |  |  |

|                         | 2.1                  | Parallel bus   |                              |          |  |  |

|                         |                      | 2.1.1          | Address Bus                  | 3        |  |  |

| 2.2 Data Bus            |                      |                |                              | 3        |  |  |

|                         | 2.3                  | Control        | Bus                          | 3        |  |  |

|                         |                      | 2.3.1          | Master Reset                 | 3        |  |  |

|                         |                      | 2.3.2          | Write Not                    | 4        |  |  |

|                         |                      | 2.3.3          | Read Not                     | 4        |  |  |

|                         |                      | 2.3.4          | Module Select 1 and 2 Not    | 4        |  |  |

|                         | 2.4                  | Testing        | and Measurement              |          |  |  |

|                         |                      | 2.4.1          | Measurements                 | 4        |  |  |

|                         |                      |                | Testing                      | 5        |  |  |

|                         | 2.5                  | =              | ane                          | 5        |  |  |

|                         |                      |                | Termination resistors        | 6<br>7   |  |  |

|                         | 2.6 Case             |                |                              |          |  |  |

|                         | 2.7                  |                | Console                      | 9        |  |  |

|                         |                      | 2.7.1          | 16550 UART                   | 9        |  |  |

|                         |                      | 2.7.2<br>2.7.3 | MAX-232                      | 10<br>10 |  |  |

|                         |                      | 2.7.3          | Demonstration Software       | 14       |  |  |

|                         | 2.8                  |                | Digital-Analog-Converter     |          |  |  |

|                         | 2.0                  | 2.8.1          | TLC 7528 Dual R2R Ladder DAC | 19       |  |  |

|                         |                      | 2.8.2          | IDT7201 CMOS FIFO Buffer     | 19       |  |  |

|                         |                      | 2.8.3          | Theory verfication           | 20       |  |  |

|                         |                      | 2.8.4          | Schematics                   | 21       |  |  |

|                         |                      | 2.8.5          | Demonstration Software       | 24       |  |  |

| 3                       | Ada                  | tressina       | DACA and DACB                | 28       |  |  |

| U                       | 3.1                  | •              | o Hardware interface         |          |  |  |

|                         | 0.1                  | 3.1.1          | Measurement error            | 31       |  |  |

| 4                       | Tov                  |                | ıre                          |          |  |  |

| +                       | 4.1                  |                | I Implementation details     | _        |  |  |

|                         | т. 1                 | Jonicia        | implomontation detaile       | <u>ل</u> |  |  |

|    |                               | 4.1.1 General definitions and pinout of the AVR                                                             | 32                                            |

|----|-------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|    |                               | 4.1.2 Read and Write routines                                                                               | 34                                            |

|    |                               | 4.1.3 UART and DAC update polling                                                                           | 34                                            |

|    | 4.2                           | DAC sound generation                                                                                        | 35                                            |

|    |                               | 4.2.1 DAC modes                                                                                             | 35                                            |

|    |                               | 4.2.2 Tones and Tracks                                                                                      | 40                                            |

|    |                               | 4.2.3 Track switching                                                                                       | 44                                            |

|    | 4.3                           | User command interpretation                                                                                 | 44                                            |

|    |                               | 4.3.1 Command structure and parsing                                                                         | 44                                            |

|    |                               | 4.3.2 Command parameters                                                                                    | 46                                            |

|    | 4.4                           | Gameplay                                                                                                    | 47                                            |

|    | 4.5                           | Memory constraints                                                                                          | 49                                            |

|    |                               |                                                                                                             |                                               |

| I  | A                             | short introduction to VHDL                                                                                  | 50                                            |

| 5  | Pre                           | erequisites                                                                                                 | 50                                            |

| 6  | Cre                           | eating a design                                                                                             | 50                                            |

| 7  |                               | mulating a design                                                                                           |                                               |

|    |                               |                                                                                                             |                                               |

| 8  | Syr                           | nthesizing a design                                                                                         | 53                                            |

|    |                               |                                                                                                             |                                               |

|    | l M                           | leta 5                                                                                                      | 54                                            |

| 9  | His                           | story                                                                                                       | 54                                            |

| 1  | 0 Too                         | oling                                                                                                       | 56                                            |

|    |                               | 1 Vendor Tools                                                                                              |                                               |

|    | 10.2                          | 2 Free Software Tools                                                                                       | 56                                            |

| 1  | 1 Par                         | ripherals                                                                                                   | 57                                            |

| •  |                               | 1 UART                                                                                                      |                                               |

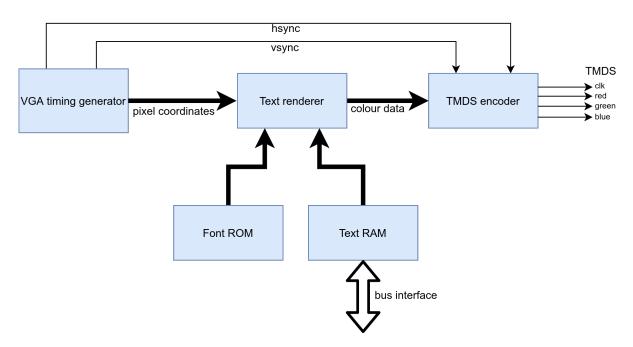

|    |                               | 2 DVI graphics                                                                                              |                                               |

|    | 11.2                          | - DVI grapinos                                                                                              | $\mathbf{v}$                                  |

|    |                               |                                                                                                             |                                               |

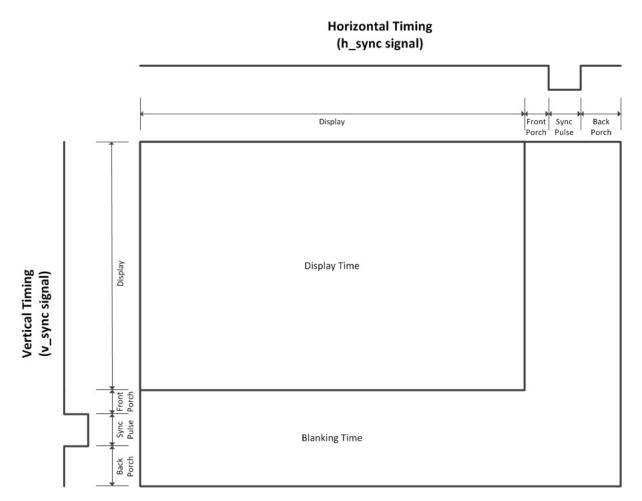

|    |                               | 11.2.1 VGA timing                                                                                           | 57                                            |

|    |                               | 11.2.1 VGA timing                                                                                           | 57<br>58                                      |

|    | 11.3                          | 11.2.1 VGA timing                                                                                           | 57<br>58<br>59                                |

|    |                               | 11.2.1 VGA timing 11.2.2 Text renderer 11.2.3 TMDS encoder 3 Ethernet                                       | 57<br>58<br>59<br>59                          |

|    | 11.4                          | 11.2.1 VGA timing 11.2.2 Text renderer 11.2.3 TMDS encoder 3 Ethernet 4 WS2812 driver                       | 57<br>58<br>59<br>59<br>60                    |

|    | 11.4<br>11.5                  | 11.2.1 VGA timing 11.2.2 Text renderer 11.2.3 TMDS encoder 3 Ethernet 4 WS2812 driver 5 DRAM                | 57<br>58<br>59<br>59<br>60<br>61              |

| 1  | 11.4<br>11.5<br>11.6          | 11.2.1 VGA timing 11.2.2 Text renderer 11.2.3 TMDS encoder 3 Ethernet 4 WS2812 driver 5 DRAM 6 External Bus | 57<br>58<br>59<br>59<br>60<br>61              |

| 1: | 11.4<br>11.5<br>11.6<br>2 Tes | 11.2.1 VGA timing 11.2.2 Text renderer 11.2.3 TMDS encoder 3 Ethernet 4 WS2812 driver 5 DRAM                | 57<br>58<br>59<br>60<br>61<br>61<br><b>62</b> |

| III | The Core                                  | 62 |

|-----|-------------------------------------------|----|

| 13  | Overview                                  | 63 |

| 14  | Control                                   | 63 |

| 15  | Decoder                                   | 64 |

| 16  | Registers                                 | 65 |

| 17  | Arithmetic and Logic Unit (ALU)           | 66 |

| 18  | Control and Status Registers (CSR)        | 66 |

| 19  | Memory Arbiter                            | 67 |

| 20  | Exception Control                         | 68 |

| 21  | Erklärung der Eigenständigkeit der Arbeit | 70 |

| I   | List of Figures                           | I  |

| П   | List of Tables                            | II |

| Ш   | Listings                                  | II |

| An  | hang                                      | ٧  |

### 1 Task description

### 1.1 Hardware

Due to the recurring questions in the environment of the Hackerspace Innsbruck about the internal workings of a computer system and the lack of material to demonstrate these, hardware should be developed for educational purposes. This hardware should not be to complex to understand but still demonstrate basic tasks of a computer system. The targeted computing tasks are human interface device controllers, under which a Digital to Analog Converter<sup>A</sup> and a serial console with TIA-/EIA-232 compliant voltage levels were chosen. For these peripherials schematics and a working implementation in the hardware building style of the hackerspace should be built. All nescessary hardware will be provided by the Hackerspace. If possible already present hardware should be used, if impossible new one will be ordered. All schematics should, whenether possible be written in open-source software such as Kicad or GNU-EDA.

If possible software-examples should be written as well, though the complexity of these was coupled to the time left to spend on the project. Software should be written in C, the coding convention is left to the implementer.

<sup>&</sup>lt;sup>A</sup>From now on reffered to simply as DAC

### 2 Hardware peripherials

### 2.1 Parallel bus

The core part of the hardware is the interface between the microprocessor and the hardware peripherials. This bus is delivering data in parallel and is therefore named the "parallel bus". This bus has 3 different sub-parts:

- 1. The address bus

- 2. The data bus

- 3. The control bus

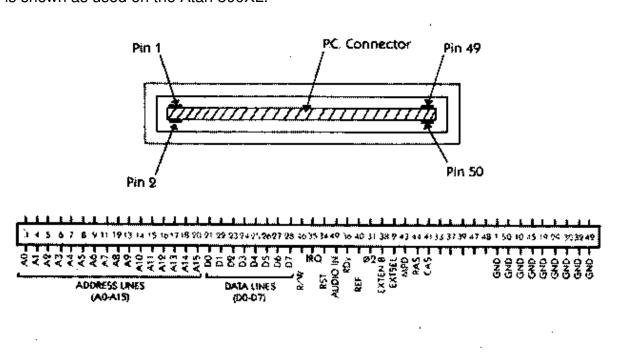

This split is common in many computer architectures and bus systems used by various microprocessor manufacturers. In figure i the layout of the Atari Parallel Bus Interface is shown as used on the Atari 800XL.

Figure 4.

Parallel Bus Pinout

Figure i: Atari PBI Pinout; Source: https://www.atarimagazines.com

### 2.1.1 Address Bus

The address bus contains the nescessary data lines for addressing the individual registers of the Serial connection and the uart. On any modern system this bus is from 16 to 64 bits wide. For our implementation the bus size was chosen to be 8 bit, which is multiple times the amount of needed address space, but is the smallest addressable unit on most microcontroller architectures and therefore easy to program with. The address bus is unidirectional.

### 2.2 Data Bus

The data bus contains the actual data to be stored to and read from registers. The data bus is, as well on most systems a multiple of 16 bits wide, but for the same reasons as the data bus, was shrunk down in our case to 8 bits. The data bus is bidirectional.

### 2.3 Control Bus

Control bus is a term which referes to any control lines (such as read and write lines or clock lines) which are neither address nor data bus. The control bus in our case needed to be 5 bits wide and consists of:

- MR ... Master Reset

- ¬WR ... Write Not

- ¬RD ... Read Not

- ¬MS1 ... Module Select 1 Not

- ¬MS2 ... Module Select 2 Not

### 2.3.1 Master Reset

A high level on the MR lane signals to the peripherials that a reset of all registers and states should occure. This is needed for the serial console and the dac.

### 2.3.2 Write Not

A low level on the  $\neg WR$  lane signals the corresponding modules that the data on the data bus should be written to the register on the address specified from the address bus.

#### 2.3.3 Read Not

A low level on the  $\neg RD$  lane signals the corresponding modules that the data from the register specified by the address on the address bus should be written to the data bus.

### 2.3.4 Module Select 1 and 2 Not

A low level on one of these lines signals the corresponding module that the data on address data and the control lines is meant for it.

### 2.4 Testing and Measurement

For functional testing and verification of implementation goals, measurements needed to be performed invarious different ways and testing software was required.

### 2.4.1 Measurements

Measurements were performed, if not noted otherwise, with the Analog Discovery 2 from Digilent as it has 16bit digital I/O Pins as well a a Waveform generator and 2 differential oszilloscope inputs[1]. These were for all nescessary measurements enough. Though due to the size and construction of the device, which can be seen in figure ii errors wer encountered while performing the measurements. These are noted on occurance.

Figure ii: Digilent Analog Discovery 2; Source: https://www.sparkfun.com/

### 2.4.2 Testing

All testing was performed with an Atmel ATMega2560 due to it's large amount of I/O pins, 5V I/O which is the more common voltage level on CMOS peripherials, way of addressing pins (8 at a time) and availability. [2] All testing software was written for this ATMega and compiled using the avr-gcc from the GNU-Project.

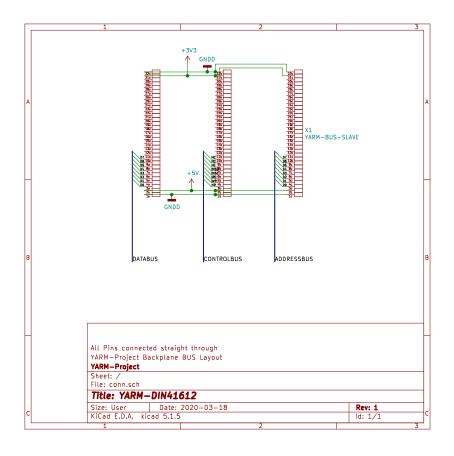

### 2.5 Backplane

To connect the modules to the microprocessor, many pins need to be connected straight through. For this purpose a backplane was chosen where DIN41612 connectors can be used. These connectors were chosen for their large pin count (96 pins) and their availability. The backplane connects all 96-pins straight through. With the 6 outer left and right pins connected for VCC and ground, as can be seen in figure iii.

Figure iii: Layout of the DIN41612 Connectors on the Backplane

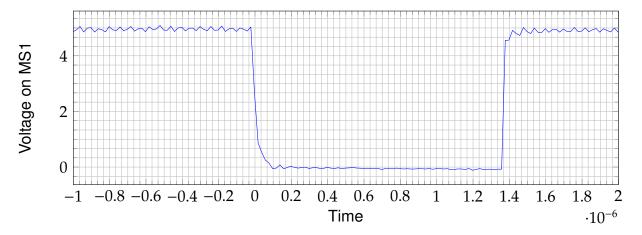

### 2.5.1 Termination resistors

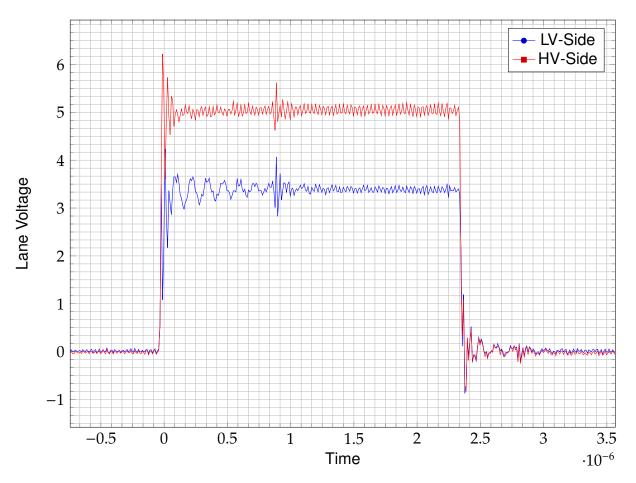

In constrast to other systems using this backplane, no termination resistors were used. This makes the bus more prone to refelctions, however these were not a problem during development with the maximum transmission rate of 1MHz, as can be seen in the sample recording in figure iv

Figure iv: Measurement at around 1MHz bus clock on MS1

The ripple seen in figure iv are most likely due to the sample rate of the Oszilloscope, which is around 10Mhz after an average filter has been applied. The measurement was performed on the finished project, with all cards installed.

### 2.6 Case

The case for the backplane was provided by the hackerspace, and is meant for installation in a rack. The case is meant for installation of cards in the EUROCARD format, therfore all modules were built by this formfactor.

Figure v: The case with installed backplane

### 2.7 Serial Console

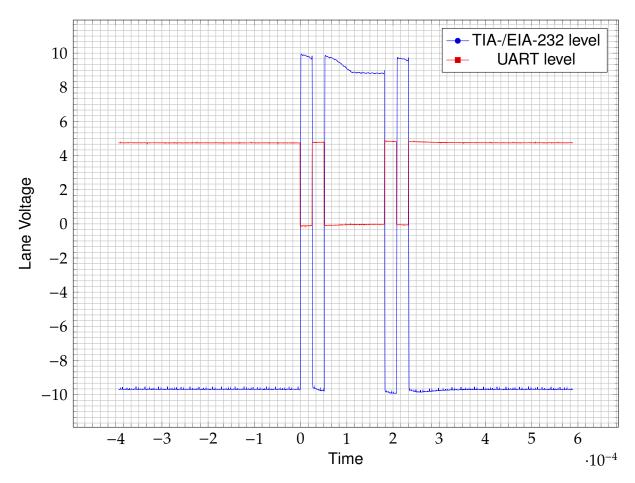

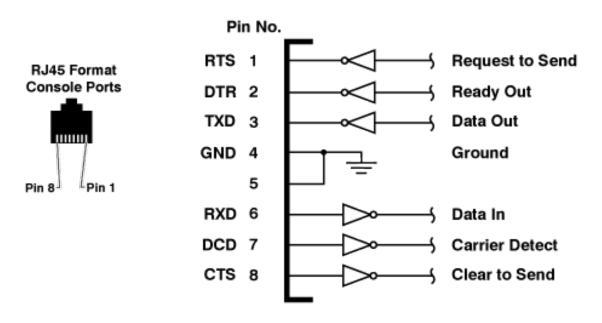

One core part of any computer systems is it's way to get human input. On older systems, and even today on server machines, this is done via a serial console. On this serial console, characters are transmitted in serial, which means bit by bit over the same line. The voltage levels used in these systems vary from 5V to 3.3V or +-10V. The most common standart for these voltage levels is the former RS-232<sup>B</sup> or as it should be called now TIA-<sup>C</sup>/EIA-<sup>D</sup>232. Voltage- levels as per TIA-/EIA Standard are not practical to handle over short distances to handle however, so other voltages are used on most interface chips and need to be converted.

#### 2.7.1 16550 UART

The 16550 UART<sup>E</sup> is a very common interface chip for serial communications. It produces 5V logic levels as output on TX and needs the same as input on RX. Thoug common for a UART, these voltage levels need to be converted to TIA-/EIA-232 levels for a more common interface.

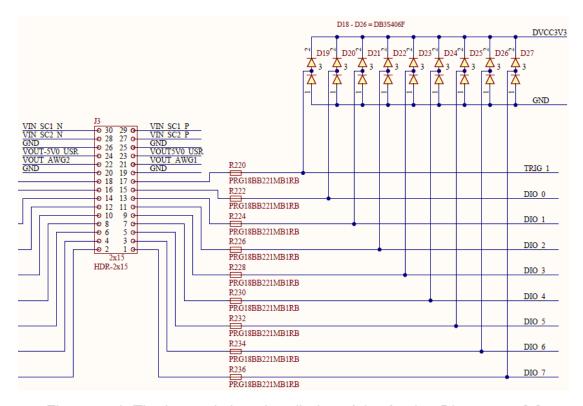

The 16550 UART is, in it's core a 16450 UART, but has been given a FIFO <sup>F</sup> buffer. It needs three address lines, and 8 data lines, which can be seen in figure vi

Figure vi: PC-16550D Pinout[3]

<sup>&</sup>lt;sup>B</sup>RS... Recommended Standard

<sup>&</sup>lt;sup>C</sup>TIA...Telecommunications Industry Association

<sup>&</sup>lt;sup>D</sup>EIA.. Electronic Industries Alliance

<sup>&</sup>lt;sup>E</sup>Uinversal Asynchronous Receiver and Transmitter

FFirst-In First-Out

In figure vi the most important lanes are the SIN and sout lanes, as they contain the serial data to and from the 16550 UART.

### 2.7.2 MAX-232

To convert the voltage levels of the 16550 UART to levels compliant wit TIA-/EIA-232 levels, the MAX-232 is used. It has two transmitters and two receivers side and generates the needed voltage levels via an internal voltage pump[4].

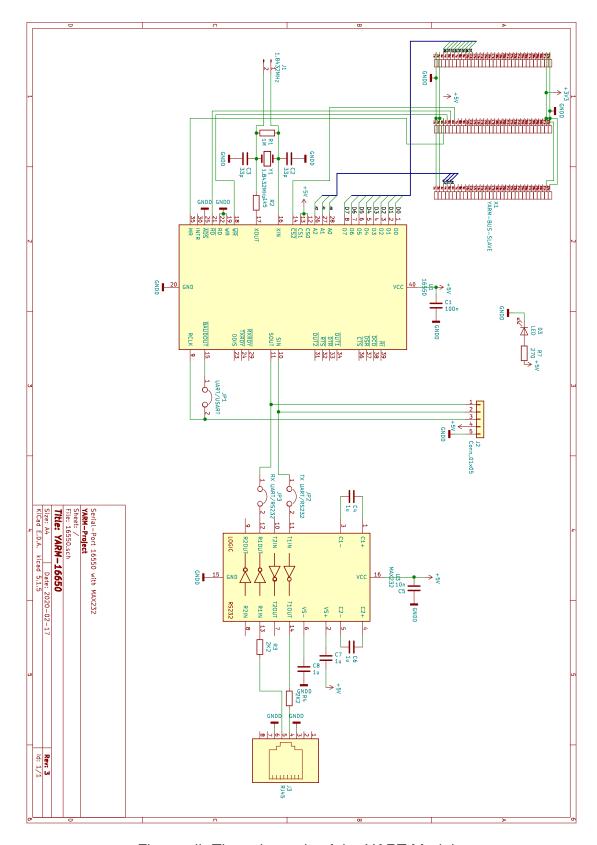

### 2.7.3 Schematics

Based on the descriptions in the datasheets the schematic in figure vii was developed.

Figure vii: The schematic of the UART Module

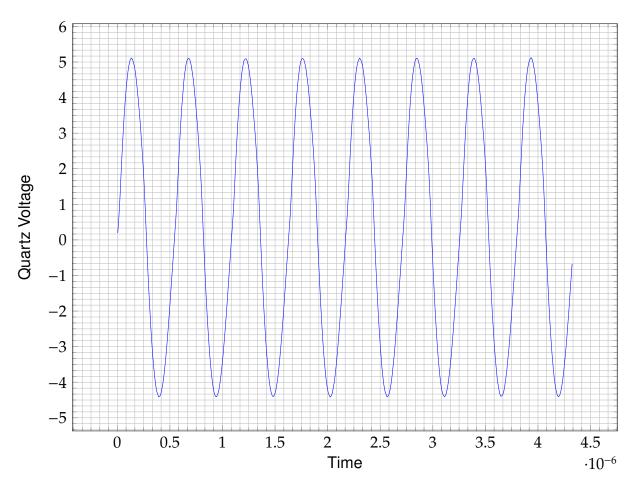

**Element Description** The quartz oszillator Y1 is the clock source for the Baud Rate generation and was chosen with 1.8432 MHz for availability reasons and because it is the lowest ozillator from which all common baud rates can still be derived from [3]. Resistors R1 and R2 are for stability and functionality of the Oszillator nescessary as per datasheet. The resulting frequency can be measured via J1, the measurement can be seen in viii. C1 is used to stabilize the voltage for the 16550 UART and is common practice. Via JP1 the UART can be transformed into a USRT where the receiver is synchronized to the transmitter via a clock line. This mode has, however, not been tested, and the clock needs to be 16 times the receiver clock rate[3]. The final output of the 16550 UART can be used and measured via J2, as shown in figure ix . Before the UART on J2 can be use however, the Jumpers JP2 and JP3 need to be removed as otherwise the MAX-232 will short out with the incoming signal. capacitors C4, C6, C7, C7 and C8 are for the voltage pump as defined in the datasheet[4]. R4 and R5 have been suggested by the supervisor in order toavoid damage to the MAX-232. The RJ-45 plug is used to transmit the TIA-/EIA-232 signal, rather than the more common D-SUB connector, because the RJ-45 connector fits on a 2.54mm grid. The Pinout onthe RJ-45 plug can be seen in figure x. C5 has the same functionality for the MAX-232 as the C1 has to the 16550-UART.

Figure viii: Measurement of the 1.8432 MHz Output on J1

Figure ix: Measurement of a character transmission before and after MAX-232

Figure x: Pinout of the RJ-45 Plug; Src: https://www.wti.com/

### 2.7.4 Demonstration Software

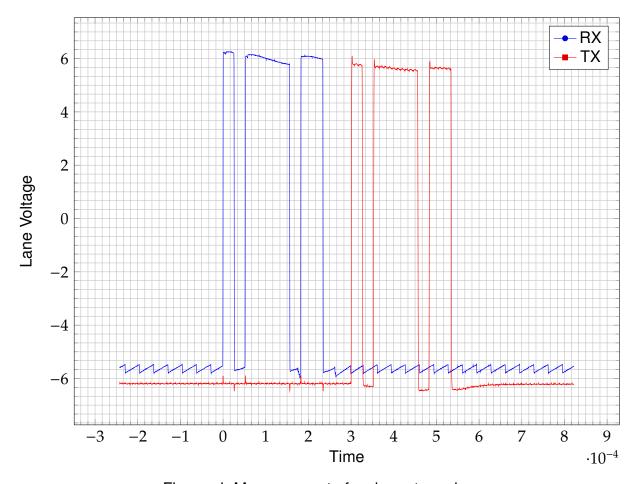

To demonstrate the functionality and prove, that the schematic has no underlying error, a program which regularly transmits a character was written as well as a simple echo program, which transmits all received characters. Both programs transmit 8 bit characters without parity at 38400 Baud. The output for program one can be seen in figure ix and the output for program two in figure xi.

Figure xi: Measurement of a character echo

**Transmit code** The transmit code regularly transmits the letter capital A via the 16550 UART, but before it can do this it needs to perform some initialisations. The functions shown in listing I are the read and write routines for accessing the 16550 UART. These routines also apply to the echo code.

```

#define F_CPU 16000000UL

#include <stdint.h>

#include <util/delay.h>

#define BUS_HOLD_US 1

```

```

/* Shift values inside the PORTL Register */

#define WR_SHIFT 1

#define RD_SHIFT 2

#define MR_SHIFT 0

#define CS_SHIFT 3

#define CS_ADC_SHIFT 4

14

/* Registers in the 16550 UART */

15

#define UART_REG_DLLS

#define UART_REG_DLMS

#define UART_REG_TXRX

0

#define UART_REG_IER

1

#define UART_REG_IIR

2

#define UART_REG_LCR

3

#define UART_REG_MCR

4

#define UART_REG_LSR

5

#define UART_REG_MSR

6

#define UART_REG_SCR

27

void set_addr(uint8_t addr){

28

29

PORTK = addr;

30

return;

31

32

void write_to_16550(uint8_t addr, uint8_t data){

35

36

set_addr(addr);

37

DDRF = 0xFF;

38

PORTL &= ~(1<<WR_SHIFT);

39

PORTF = data;

40

PORTL &= ~(1<<CS_SHIFT);

42

_delay_us(BUS_HOLD_US);

43

PORTL |= 1<<CS_SHIFT;

45

set_addr(0x00);

46

PORTL |= 1<<WR_SHIFT;

PORTF = 0x00;

48

return;

49

50

51

uint8_t read_from_16550(uint8_t addr){

52

53

```

```

uint8_t data = 0 \times 00;

54

set_addr(addr);

55

DDRF = 0 \times 00;

56

PORTF = 0x00;

57

PORTL &= ~(1<<RD_SHIFT);

58

PORTL &= ~(1<<CS_SHIFT);

59

_delay_us(BUS_HOLD_US);

60

data = PINF;

61

PORTL |= 1<<CS_SHIFT;

62

set_addr(0x00);

63

PORTL |= 1<<RD_SHIFT;

64

DDRF = 0xFF;

65

PORTF = 0x00;

66

_delay_us(BUS_HOLD_US); /*Wait for the data and signal lanes to become

stable*/

return data;

68

69

```

Listing I: Read and write routines for the 16550 UART

To write to the 16550 UART, you need to perform some setup tasks. After startup, it requires a MR for at least 5 $\S$ s[3]. The baud rate divisor latch needs to be set to the specified divisor for the desired baud rate, and the character width and parity control needs to be set. The MR signal is beeing generated by the AVR on bootup. To access the divisor latch, the divisor latch access bit needs to be set and after setting up the baud rate divisor latch, it nees to be cleared to allow a regular transmission. This process can be seen in listing II

```

int main(){

2

/* Disable interrupts during initialisation phase */

3

cli();

5

/* Setup Data Direction Registers and populate with same default

6

values */

DDRF = 0xFF; /* Data Bus */

8

DDRK = 0xFF; /* Address Bus */

9

DDRL = 0xFF; /* Control Bus */

10

11

PORTF = 0x00;

PORTK = 0x00:

12

PORTL = 0x00;

13

/* Cleanly reset the 16550 uart */

15

PORTL |= (1<<WR_SHIFT);

16

PORTL |= (1<<RD_SHIFT);

17

PORTL |= (1<<CS_SHIFT);

18

```

```

PORTL |= (1<<MR_SHIFT);

19

_delay_us(100);

20

PORTL &= ~(1<<MR_SHIFT);

21

22

_delay_us(1000);

23

sei();

24

for(;;){

26

write_to_16550(UART_REG_LCR,0x83);

write_to_16550(UART_REG_DLLS,0x03);

write_to_16550(UART_REG_DLMS,0x00);

29

write_to_16550(UART_REG_LCR,0x03);

30

write_to_16550(UART_REG_TXRX,'A');

31

_delay_us(10000);

}

33

34

return 0;

36

```

Listing II: 16550 INIT routines and single char transmission

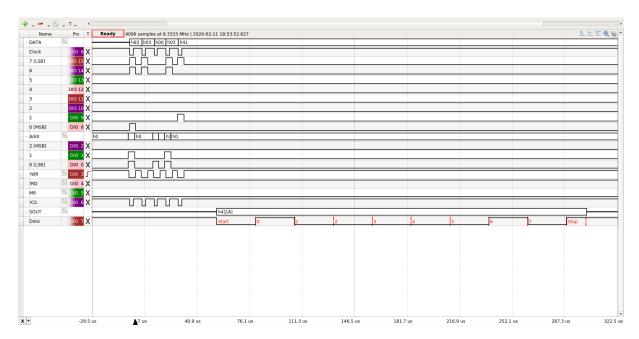

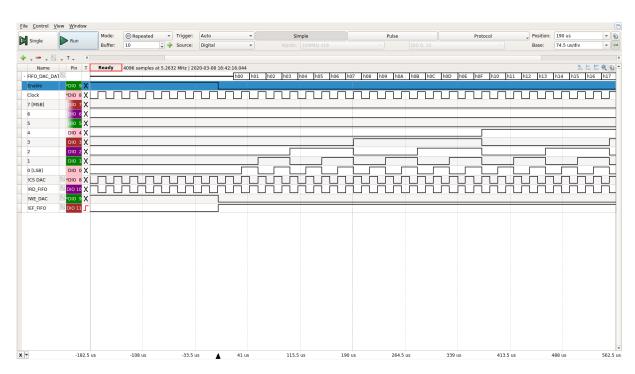

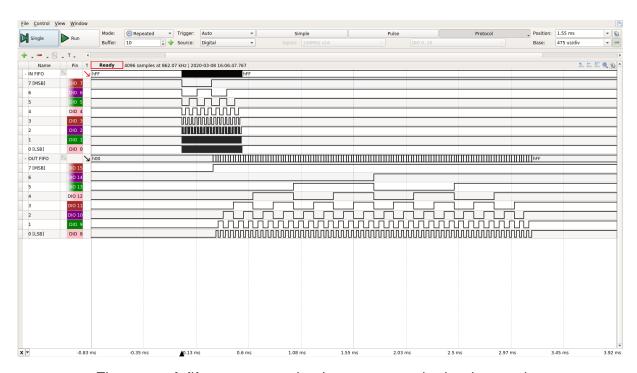

The output of this code on the address, data and control bus as well as on the SOUT lane of the 16550 UART can be seen in figure xii

Figure xii: Transmission of character A via the 16550 UART

**Echo code** The echo code permanently polls the 16550 UART wether a character has been received, and if yes, reads it from the receiver holding register andwrites it back to the tx holding register. The output of this code can be seen in figure xi. The

initialisation is practically the same as for the transmission code, as well as the read and write routines in listing I.

```

int main(){

2

/* Disable interrupts during initialisation phase */

3

cli();

5

/* Setup Data Direction Registers and populate with same default

6

values */

DDRF = 0xFF; /* Data Bus */

8

DDRK = 0xFF; /* Address Bus */

9

DDRL = 0xFF; /* Control Bus */

10

11

/* Cleanly reset the 16550 uart */

PORTL |= (1<<WR_SHIFT);

13

PORTL |= (1<<RD_SHIFT);

PORTL |= (1<<CS_SHIFT);

PORTL |= (1<<CS_ADC_SHIFT);

16

PORTL |= (1<<MR_SHIFT);

17

_delay_us(100);

18

PORTL &= \sim(1<<MR_SHIFT);

19

_delay_us(1000);

20

write_to_16550(UART_REG_LCR,0x83);

22

write_to_16550(UART_REG_DLLS,0x03);

23

write_to_16550(UART_REG_DLMS,0x00);

write_to_16550(UART_REG_LCR,0x03);

25

for(;;){

26

if(read_from_16550(UART_REG_LSR) & 0x01){

write_to_16550(UART_REG_TXRX,

28

read_from_16550(UART_REG_TXRX));

29

}

30

}

31

32

return 0;

33

34

```

Listing III: 16550 character echo

### 2.8 Audio Digital-Analog-Converter

A digital to analog converter takes a digital number and converts it to a analog signal. The output of one such conversion is called a sample. With enough samples per second various different waveforms can be produced which, when amplified and put

onto a speaker, can be heared by the human ear as a tone. With various tones in series a melody can be produced, which is what the DAC in this implementation does.

### 2.8.1 TLC 7528 Dual R2R Ladder DAC

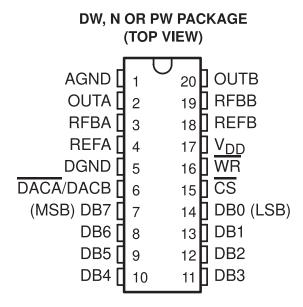

The TLC 7528 is a Dual output Parallel input R2R Ladder DAC with a maximum sample rate of 10MHz[5] and which (should be) is monotonic over the entire D/A Conversion Range. The TLC-7528 was the only component chosen, where availability was not a factor, but rather due to it's design. It is the cheapest dual R2R Ladder dac which takes **PARALLEL** input, which was an important feature, because the backbone of the project is its parallel bus. Further the DAC was developed for audio aplications[5] obvious and the TLC-7528 was the only IC available as DIP <sup>G</sup>, of which the pinout can be seen in figure xiii

Figure xiii: TLC-7528 Pinout[5]

### 2.8.2 IDT7201 CMOS FIFO Buffer

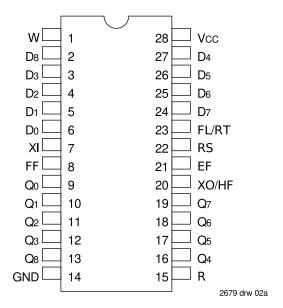

The IDT7201 is an asychronous CMOS FIFO, which means that it can be read with a completely independant speed from which it is written and vice versa. It has 9 bit words, which can be seen in figure xiv, and can store up to 256 words[6]. It is used as a buffer to store data describing the targeted waveform in order to free time on the parallel bus for interaction with the 16550 UART.

<sup>&</sup>lt;sup>G</sup>DIP... Dual Inline Package

Figure xiv: IDT-7201 Pinout[6]

### 2.8.3 Theory verfication

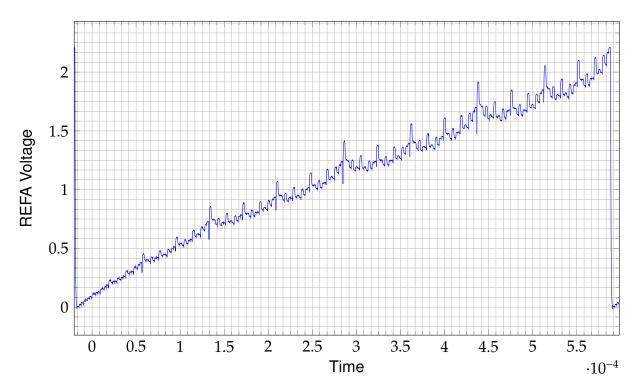

Before tests of the complete unit were conducted, the functionality of the device and the validity of the knowledge of operations were performed. For that the DAC was directl connected to the ATMega without the FIFO infront of it. A saw was generated on only the DACA channel, which was put into voltage mode as described in the datasheet[5] and seen in figure xv. After the result seen in xvi was found a lot of effort was put in to determine the source of the heavy noise, however no obvious conclusion can be made, execpt that it comes from the DAC itself and is consistant over whatever frequency used. A damaged IC could be the reason or a sloppy production progress. Filters can be used to reduce the noise, however this was not done in this thesis, as the generated audio does not seem to suffer from these non-linearities as badly as when measured standalone.

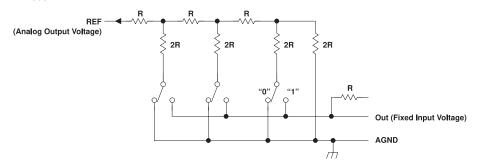

#### voltage-mode operation

It is possible to operate the current multiplying D/A converter of these devices in a voltage mode. In the voltage mode, a fixed voltage is placed on the current output terminal. The analog output voltage is then available at the reference voltage terminal. Figure 11 is an example of a current multiplying D/A that operates in the voltage mode.

Figure 11. Voltage-Mode Operation

The following equation shows the relationship between the fixed input voltage and the analog output voltage:  $V_O = V_I (D/256)$

Figure xv: TLC-7528 in voltage modet[5]

Figure xvi: Measurement of a generated SAW signal via the TLC7528

### 2.8.4 Schematics

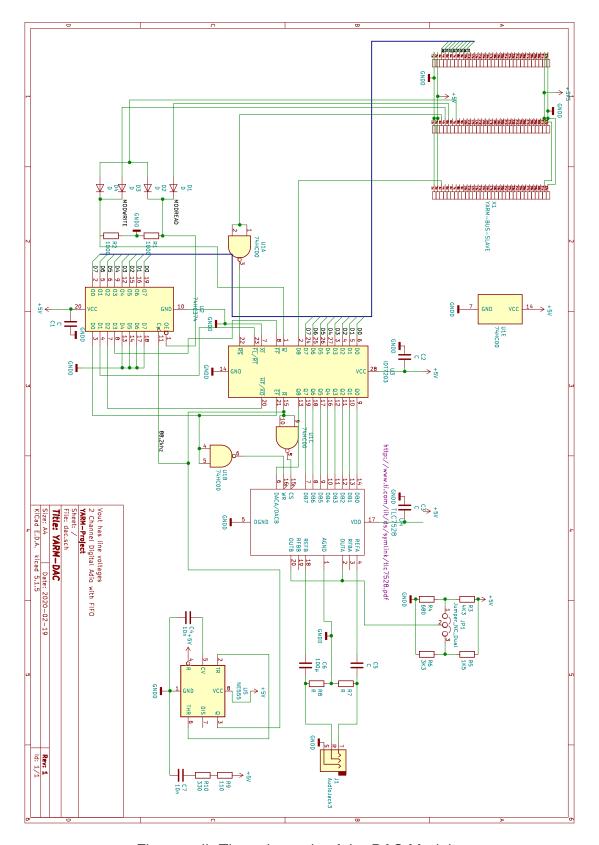

Based on the descriptions in the datasheets the schematic in figure xvii was developed.

Figure xvii: The schematic of the DAC Module

**Element Description** Diodes D1 through D4 are used as OR-Gates in conjunction with R1 and R2 to generate the  $\neg MODRD$  and  $\neg MODWR$  signals for the D Flip-Flop <sup>H</sup> and FIFO respectively, by these formulas:

$$\neg MODRD = \neg RD \lor \neg MS2$$

$$\neg MODWR = \neg WR \lor \neg MS2$$

On a read access, the output enable of the D-Latch becomes low, which writes the status bits of the FIFO onto the data bus. C1, C2 and C3 are for stability reasons and are good practice, similar to the UART module. 74HC00 is a quad NAND-Gate[8] which is only used for inversion, chosen, like the 74HC374, for availability reasons. The A part of the NAND-Gate inverts the MR signal from the bus to a MR signal as the FIFOs reset is low active. The B part of the NAND-Gate inverts the FIFO Empty flag. It's output is connected to the  $\neg WR$  input of the DAC, which means that the DAC doesn't convert the input anymore, if the FIFO Empty flag is set to low.

The NE555 generates the audio clock signal, which should be the double of 44.1kHz<sup>1</sup> as 44.1kHz is the standard samling rate of CD-Audio[9]. Resistors R9 and R10 together with C7 form the Oscillator part of the NE55. C4 is for stability reasons and doesn't define the frequency of the oscillator.

The generated clock is used for the  $\neg R$  of the FIFO and inverted on the DAC, which makes the data available on the output before being stored into the DAC as it receives the signal to store the data after the FIFO makes it available on the bus.

The DAC is operated in voltage mode as described in xv, with it's voltage source beeing available at either 3.472Vpp for professional audio or 0.894Vpp for consumer audio, as defined per convention.[10] The voltage source can be controlled via Jumper JP1.

C5 and C6 together with the load resistance on the audio jack form a high pass with a cutoff frequency of

$$f_C = \frac{1}{2\pi RC} = \frac{1}{2\times \pi \times 10K\Omega \times 100\mu F} = 0.159154943Hz$$

which should cover the hearable spectrum. The high pass was needed to generate a positive and negative half of the wave form, as the DC-Offset with a frequency of 0Hz is orders of magnitudes lower than the  $f_C$  of the highpass gets filtered away.

R7 and R8 have been installed in order to unload the capacitors after device poweroff.

H74HC374[7]

<sup>&</sup>lt;sup>1</sup>Because we have 2 output channels

**NE55 Clock Source** Though used as a clovk source, the NE555 is a bad clock source if a stable clock is needed, because it varies widely with temperature, preasure and aging elements. A better solution would have been a quartz which is divided down to the desired frequency, whichwas what CD Drives used to do, but more commonly in modern CD Drives, an ASIC with internal PLL is used, thus the required quartz can no longer be sourced.

### 2.8.5 Demonstration Software

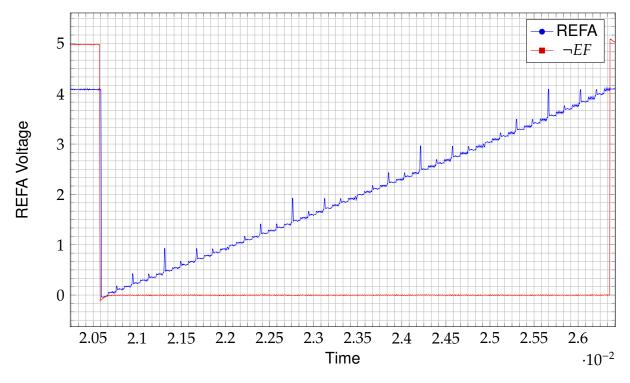

**SAW Generator** To prove read and write access from the D Flip-Flop and the FIFO are working, the same saw signal has been generated as in figure xvi , however the signal was put into the FIFO and not the DAC directly. The resulting saw wave can be seen in figure xviii together with the FIFO Empty flag. The FIFO Empty flag, as explained before, is inverted and starts/ends the complete D/A conversion, until further data is received.

Figure xviii: Measurement of a generated SAW signal with the FIFO Empty flag

The time difference betwen a stor and complete write cycle can be seen in figure xx, while the figure xix shows the transmission between dac and fifo in more detail.

Figure xix: A transmission between the FIFO and the DAC

Figure xx: A fifo store operation in contrast to the load operation

The initialisation routines and read/write operations for the DAC module are basically the same as for the UART module, and have thus been ommitted. They can be seen in listing II and partially in listing II.

```

int routine(){

```

```

for(uint8_t i = 0; i < 0xFF; i++){

write_to_dac(0x00, i);

}

write_to_dac(0x00, 0x00);

delay_ms(10);

return 0;

}</pre>

```

Listing IV: SAW Generation for the DAC with FIFO

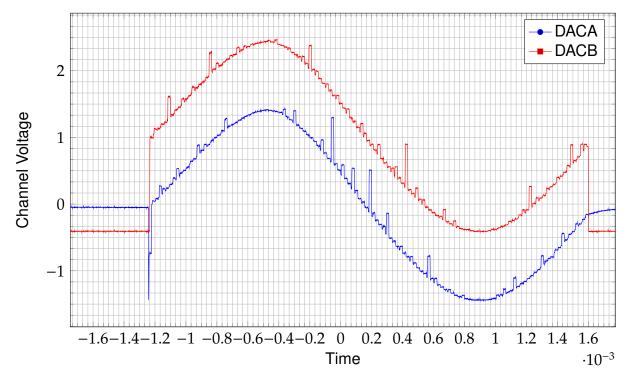

**Sine Generator** As a further example a sine was generated and played on the DAC. The ATMega itself is not powerful enough to generate the sine on the fly, therefore a lookup-table had to be generated, which can be seen in listing V. How the data is transmitted to the FIFO can be seen in listing VI and figure xxi and the resulting sine on both output channels can be seen in figure xxii.

Listing V: Sine LUT Generation

The look-up table has a size of 256, which is the maximum value an 8 bit integer can take. This size was chosen to make operation faster as it only takes one cycle to load an array value into a register and another one to store it into the GPIO register. The sine table in further examples was pre-genrated on the compiling host to reduce startup time. The mothod shown in listing V is not fast due to the lack of a floating point unit on the AVR. [2]

```

int routine(){

for(uint8_t i = 0; i < 0xFF; i++){

write_to_dac(i%2, sine_table[i]);

}

write_to_dac(0x00, 0x00);

write_to_dac(0x01, 0x00);

delay_ms(10);

return 0;</pre>

```

12 }

Listing VI: DAC Sine Generation

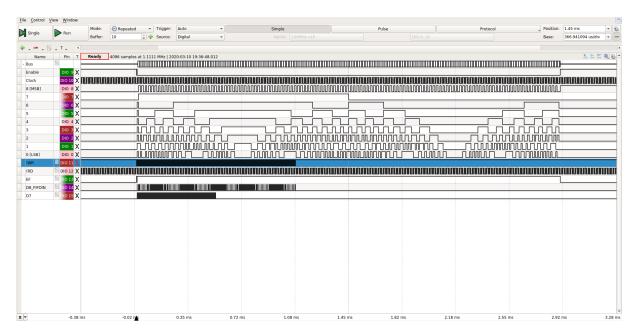

Figure xxi: Storage and retrieval of a sine to and from the FIFO

Figure xxii: Measuremet of the generated sine from the sine LUT on DACA and DACB

### 3 Addressing DACA and DACB

The DAC used has 2 output channels which can be selected by the  $\neg DACA/DACB$  pin as seen in figure xiii. This pin was mapped to bit 0 of the address bus in order to make use of it. Bit 8 on the fifo was used to store the bit. It was not implemented with half the bus clock to make both channels independent of each other. This however uses more time on the backend because it means the fifo is used up at twice the speed. No current example makes use of this, but it may be used in future examples and implementations on this unit.

On the audio jack DACA is mapped to the right channel and DACB to the left channel.

### 3.1 FPGA to Hardware interface

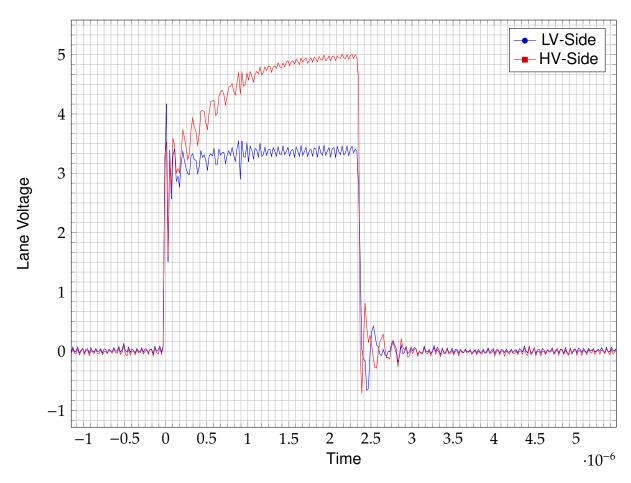

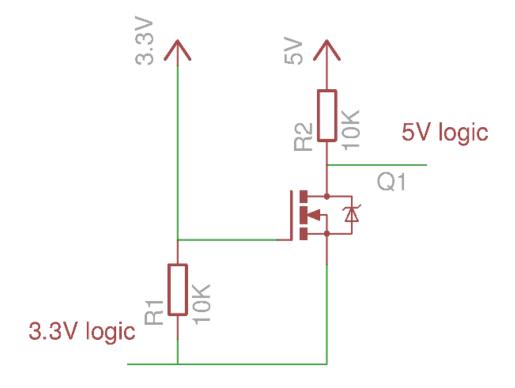

To make the Hardware work with the FPGA's 3.3V I/O, level shifter have been installed and a FPGA module was built. This module maps the IO/Pins in a similar way to the ATMega 2560 used in examples before. The bidirectional 5V<->3.3V logic level converters have been obtained on amazon, and have not been well documented. Their functionality has been tested and verified in both directions, which can be seen in figures xxiii and xxiv. The schematic has also been determined through measurements with a multimeter and the schematic in figure xxv shows similar resistor values in the same configuration [11].

Figure xxiii: 3.3V to 5V conversion using the level shifter

The in figure xxiii shown output on the HV side, corresponds with the schematics in figure xxv where it can be seen that the resistor R2 is loading the bus capacitance to a 5V high state.

Figure xxiv: 5V to 3.3V conversion using the level shifter

Figure xxv: The internal schematics of the level shifter[11]

#### 3.1.1 Measurement error

During an attempt to measure wether the level shifters in the final module were working, a measurement between the LV and the HV side showed only a difference of 0.7V. After some troubleshooting, it was found that the Analog Discovery has clamping diodes against the 3.3V rail shown in figure xxvi. These diodes produce the 0.7V offset and prevent the parallel bus from rising to 5V when a digial I/O pin of the Analog Discovery 2 is connected to the bus. [12].

Figure xxvi: The internal clamping diodes of the Analog Discovery 2[1]

## 4 Textadventure

To illustrate how the components work together and can be used in various different applications, a small text-adventure with audio effects was written in C. The main goal was to show the capabilities of even small systems like the one developed.

# 4.1 General Implementation details

# 4.1.1 General definitions and pinout of the AVR

Like the before examples, the textadventure was implemented on an ATMega2560 and uses 3 different Registers for transmission: PORTF, PORTK and PORTL for address bus, data bus and control bus respectively, as can be seen in listing VII

```

/* Copyright (C) 2020 tyrolyean

2

* This program is free software: you can redistribute it and/or modify

3

* it under the terms of the GNU General Public License as published by

* the Free Software Foundation, either version 3 of the License, or

* (at your option) any later version.

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

10

* GNU General Public License for more details.

11

12

* You should have received a copy of the GNU General Public License

13

* along with this program. If not, see <a href="http://www.gnu.org/licenses/">http://www.gnu.org/licenses/>.</a>

14

*/

16

#ifndef _AVR_H_TEXT

17

#define _AVR_H_TEXT

19

20

21

#define F_CPU 1600000UL

#include <avr/io.h>

24

/* Shift values for the peripherials on the control bus PORTL */

26

#define MR_SHIFT

0

#define WR_SHIFT

1

#define RD_SHIFT

2

#define CS_UART_SHIFT 3

#define CS_DAC_SHIFT 4

#define ADDR_REG

PORTK

#define DATA_REG

PORTF

#define CTRL_REG

PORTL

#define ADDR_DDR_REG

DDRK

#define DATA_DDR_REG

DDRF

#define CTRL_DDR_REG

DDRL

40

/* Included here to prevent accidental redefinition of F_CPU */

41

#include <util/delay.h>

/* Time it takes for the bus lanes to become stable for read and write

access */

#define BUS_HOLD_US 1

```

```

void set_addr(uint8_t addr);

#endif

void set_addr(uint8_t addr);

#endif

```

Listing VII: The avr.h header file

The in listing VII shown preprocessor macros MR\_SHIFT, WR\_SHIFT, RD\_SHIFT, CS\_UART\_SHIFT and CS\_DAC\_SHIFT are used to indicate the position of the corresponding control lines inside the control bus register. All other shift values are the same bitordering in input as in output.

The BUS\_HOLD\_US is used to tell the avr how many microsecons it takes for the data bus to be latched into input register of the devices on write or how long it takes for the data bus to become stable on read. A delay of less than 1 microsecond is not possible due to limitations of the AVR and the bus capacity, which increases the BER<sup>J</sup> to a level which effects regular operation.

#### 4.1.2 Read and Write routines

The set\_addr function is the same as in the UART example code in listing I and has therefore been omitted, execept for its definition in the avr.h file in listing VII. The read and write functions for the UART module and the DAC module are the same as in the example code for the modules and have been ommitted therefore as well.

#### 4.1.3 UART and DAC update polling

The AVR constantly polls the DAC and UART modules for updates as can be seen in listing VIII. The routine\_MODULE functions poll their respective modules for updates as can be seen in listings IX and X. When a character is received, it is stored inside a bufer array and regular operation continues. If the  $\neg EF$  status bit is set in a read from the dac, the feed\_dac function is called which stores 256 bytes into the DAC and regular operation continues.

```

int routine(){

routine_dac();

routine_uart();

routine_game();

```

JBER...Bit Error Ratio

```

return 0;

```

Listing VIII: The routine function looped by the main

```

void routine_uart(){

2

uint8_t received = read_from_uart(UART_REG_LSR);

3

if(received & 0x01){

4

received = read_from_uart(UART_REG_TXRX);

ingest_user_char(received);

6

if(received == '\r'){

writechar_16550('\n');

writechar_16550(received); /* Echo back */

10

}

11

12

return;

13

14

```

Listing IX: The routine function for the UART

```

void routine_dac(){

uint8_t received = read_from_dac(0x00);

if(!(received & (0x01<<0))){

feed_dac();

}

return;

}</pre>

```

Listing X: The routine function for the DAC

# 4.2 DAC sound generation

#### 4.2.1 DAC modes

The DAC can produce any waveform described by 8 bit unsigned PCM code. Though possible to feed predefined waveforms into the DAC, the AVR doesn't have enough onboard memory to store more than a few seconds of these waveforms.

For example to store one second of 8 bit unsigned PCM Code at 2 times 44.1KHz sampling rate of the DAC, the AVR would have to store  $s=2\times 44100\frac{Bytes}{s}*1s=2\times 44100Bytes=88.2KB$ , but it has only a total of 256KB of onboard flash[2] which makes for a total track length of  $t=\frac{256KB}{88.2\frac{KB}{2}}=2.9s$  with only one track.

Therefore the AVR generates the audio on runtime. To do that it has 6 builtin modes in which it can run, as can be seen in listing XI:

- 1. silent mode: The DAC produces no output at all and is completely silent.

- 2. sine mode: The DAC produces a sine with a specific frequency and an amplitude of 255.

- 3. square mode: The DAC produces a square wave with a specific frequency and an amplitude of 255.

- 4. saw mode: The DAC produces a saw wave with a specific frequency and an amplitude of 255.

- 5. noise mode: The DAC produces a pseudo-random white-noise with a maximum amplitude of 255.

- 6. triangle mode: The DAC produces a triangle wave with a specific frequency and an amplitude of 255.

To perform these tasks the DAC takes two parameters, again seen in listing XI:

- A frequency deviation: Used to tell the dac how much the desired frequency deviates from the base frequency of each waveform.

- A mode: Used to tell it which waveform to generate

```

/* The operation modes of the dac used for generation of different tones */

#define DAC_MODE_SILENT

#define DAC_MODE_SINE

1

#define DAC_MODE_SQUARE

2

#define DAC_MODE_SAW

3

#define DAC_MODE_NOISE

#define DAC_MODE_TRIANGLE

extern uint8_t dac_mode;

/* This variable is used to deviate the frequency from the baseline

frequency

* of around 1kHz. If this integer is positive it makes the produced

waveform

* longer, if it is negative the produced waveform becomes less sharp, but

12

* frequency goes up. 0 is the baseline */

extern int16_t dac_frequency_deviation;

```

Listing XI: The DAC operation modes

```

void feed_dac(){

/* Internal counter for positioning inside the currently playing

2

* waveform */

3

static uint8_t threash = 0x00;

4

/* Used to generate the desired frequency offset if the waveform should

5

* be made "longer" --> the frequency made lower from baseline

6

static int16_t freq_delay_cnt = 0x00;

8

switch(dac_mode){

9

10

default:

11

case DAC_MODE_SILENT:

12

for(uint8_t i = 0; i < 0xFF; i++){

13

write_to_dac(i%2, 0);

14

}

15

16

break;

17

18

case DAC_MODE_SINE:

19

/* Generates a sine from a predetermined sine table in program

20

* space */

21

for(uint8_t i = 0; i < (0xFF/2); i++){

22

write_to_dac(1,

23

pgm_read_byte(&sine_table[threash]));

24

write_to_dac(0,

25

pgm_read_byte(&sine_table[threash]));

26

27

if(dac_frequency_deviation >=0){

28

freq_delay_cnt++;

29

if(freq_delay_cnt >=

30

dac_frequency_deviation){

31

freq_delay_cnt = 0;

32

threash++;

33

34

}

35

36

}else{

37

threash -= dac_frequency_deviation;

38

}

39

40

}

41

break:

42

case DAC_MODE_SQUARE:

43

/* Generates a square wave tone */

44

for(uint8_t i = 0; i < (0xFF/2); i++){

45

if(threash > (0xFF/2)){

46

```

```

write_to_dac(1, 0xFF);

48

}else{

49

50

write_to_dac(0, 0);

write_to_dac(1, 0);

51

}

52

if(dac_frequency_deviation >=0){

53

freq_delay_cnt++;

54

if(freq_delay_cnt >=

55

dac_frequency_deviation){

freq_delay_cnt = 0;

57

threash++;

58

59

}

60

61

}else{

62

threash -= dac_frequency_deviation;

}

64

}

65

break;

66

case DAC_MODE_SAW:

67

/* Generates a saw wave tone */

68

for(uint8_t i = 0; i < (0xFF/2); i++){

69

write_to_dac(0, threash);

70

write_to_dac(1, threash);

71

if(dac_frequency_deviation >=0){

freq_delay_cnt++;

73

if(freq_delay_cnt >=

74

dac_frequency_deviation) {

75

freq_delay_cnt = 0;

76

threash++;

78

}

79

80

}else{

81

threash -= dac_frequency_deviation;

82

}

83

}

break:

85

case DAC_MODE_NOISE:

86

/* Generates white noise from a predetermined LUT

87

88

for(uint8_t i = 0; i < (0xFF/2); i++){

89

static uint16_t noise_cnt = 0;

90

write_to_dac(1,

91

pgm_read_byte(&noise_table[noise_cnt]));

92

write_to_dac(0,

93

```

write\_to\_dac(0, 0xFF);

47

38

```

pgm_read_byte(&noise_table[noise_cnt]));

94

95

noise_cnt++; /* Doesn't have frequency diversion

96

97

if(noise\_cnt >= 1024){

98

noise\_cnt = 0;

99

}

100

101

}

break;

103

case DAC_MODE_TRIANGLE:

104

/* Generates a triangle wave tone */

for(uint8_t i = 0; i < (0xFF/2); i++){

106

static int8_t direction = 1;

107

if((threash == 0xFF) | !threash){

108

direction = -direction;

109

}

110

write_to_dac(0, threash);

111

write_to_dac(1, threash);

112

if(dac_frequency_deviation >=0){

113

freq_delay_cnt++;

if(freq_delay_cnt >=

115

dac_frequency_deviation) {

116

freq_delay_cnt = 0;

117

118

threash += direction;

119

120

}

121

122

}else{

123

if((dac_frequency_deviation *

124

direction) >

125

(0xFF - threash)){

126

threash = 0xFF;

127

continue;

128

129

threash = (dac_frequency_deviation *

130

direction);

131

}

132

break;

134

}

135

136

return;

137

138

```

Listing XII: The DAC waveform generation code

#### 4.2.2 Tones and Tracks

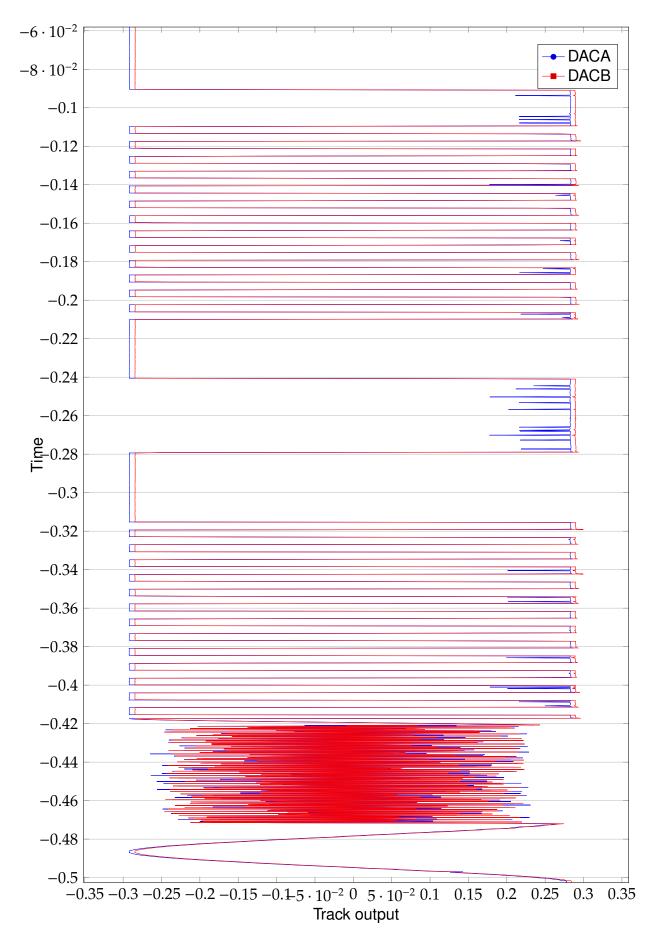

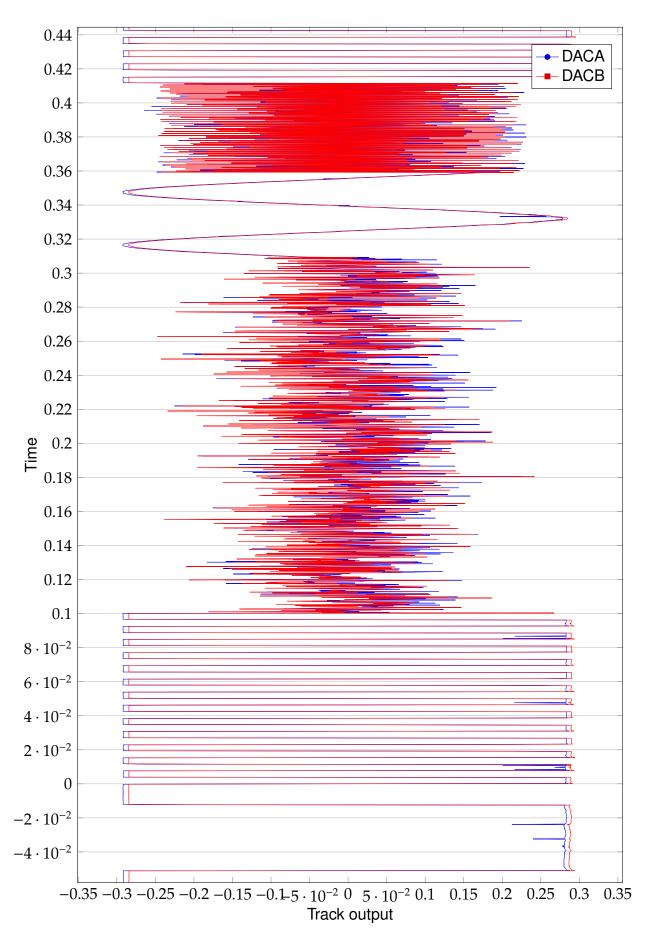

A sound track inside the textadventure consists of independent tones. A tone is a waveform at a specific frequency played for a specific time. To perform the specific time functionality independant of DAC speed, an ISR <sup>K</sup> on the AVR was used to change to the next tone every millisecond. A track is an array of tones with an end marker tone at the end which is a tone with a length of 0ms. The end marker tone tells the ISR to reset to the initial tone. The ISR can be seen in listing XIII and the sound update function, which actually updates the current tone and is responsible for playing a track in listing XIV. The output of an example track can be seen in figures xxvii and xxviii.

```

ISR(TIMER0_COMPA_vect)

{

update_sound();

}

```

Listing XIII: The ISR which fires every millisecond

```

* Loops a track indefinitely and changes voices according to predefined

st A new track resets the internal state. A voice with a length of 0ms is

* to mark the end of a track and continue at the beginning

3

void update_sound(){

6

static uint16_t audio_time = 0;

7

static size_t tone_pointer = 0x00;

8

static struct tone_t current_tone = {DAC_MODE_SILENT, 0,0};

9

if(current_track == NULL){

10

/* ABORT */

audio_time = 0 \times 00;

12

return;

13

}

14

audio_time++;

15

static const struct tone_t * old_track = NULL;

16

17

18

if(audio_time >= current_tone.length ||

current_track != old_track){

19

20

if(old_track != current_track){

21

tone_pointer = 0;

22

audio_time = 0 \times 00;

23

old_track = current_track;

24

```

KISR...Interrupt Service Routine

```

}

25

memcpy_P(&current_tone,&(current_track[tone_pointer]),

26

sizeof(current_tone));

27

28

if(current_tone.length == 0){

29

tone_pointer = 0;

30

memcpy_P(&current_tone,&(current_track[tone_pointer]),

sizeof(current_tone));

32

33

}

35

dac_mode = current_tone.waveform;

36

dac_frequency_deviation = current_tone.frequency_deviation +

37

global_frequency_offset;

audio_time = 0x00;

39

tone_pointer++;

40

}

return;

43

```

Listing XIV: The sound update function

Figure xxvii: The output of an example track part 1

Figure xxviii: The output of an example track part 2

## 4.2.3 Track switching

To switch tracks on different actions, there is a map of tracks associated with rooms. Every room has an associated track, where the association can change on actions performed, which allows for a game atmosphere change. Track changes are performed outside the ISR, which could theoretically result in a race condition where the ISR would load a faulty track for 1ms if the track change was not performed fast enough, but this is prevented by disabling global interrupts during a track change.

# 4.3 User command interpretation

## 4.3.1 Command structure and parsing

As in other text adventures [13] a command consits of one line of input terminated by a newline or line feed character \n. The carriage return character which is sometimes transmitted with a line feed character is not parsed in this text adventure. Incoming character parsing can be seen in listings IX and XV.

As one command is parsed each part is required to be separated by an empty space character which is ascii code 32 [14]. The first part of the given input is then compared to an array of actions a user can perform, for example use or search, as can be seen in listing XVI

In listing IX the comment echo back can be seen. The write\_char function before it writes the last received character back to the terminal which sent it. This is done to write what the user typed out to the terminal as otherwise it would not be seen what has been typed on any VT100 compatiable terminal[15] or terminal emulator.

```

void ingest_user_char(char in){

if(in == 0x7F /* DELETE CHAR */){

command_buffer[command_buffer_pointer--] = 0x00;

}else{

command_buffer[command_buffer_pointer++] = in;

}

return;

}

```

Listing XV: The character ingest function

The in listing XV shown branch overrides the last received character with 0x00 which

is ascii NUL and decrements the buffer pointer by one if the received character was 0x7F. 0x7F is the ADCII DELETE character [14] which instructs the receiving end that the last received character was a mistake and should be purged. This is also what a vt100 compiant terminal emulator sends when the backspace or delete key is pressed [15].

```

void routine_game(){

2

if(command_buffer_pointer >= sizeof(command_buffer)){

3

command\_buffer\_pointer = 0x00;

5

memset(command_buffer, 0, sizeof(command_buffer));

println("\nToo much input!");

8

return;

}

10

11

if(command_buffer[command_buffer_pointer-1] == '\n' ||

12

command_buffer[command_buffer_pointer-1] == '\r'){

13

/* A command from the user has been received, we are ready to

* do something!*/

16

int8_t action_id = -1;

17

for(size_t i = 0; i < sizeof(action_table)/sizeof(const char*);</pre>

18

i++){

19

if(strncasecmp(action_table[i], command_buffer,

strlen(action_table[i])) == 0){

21

action_id = i;

22

break;

23

}

24

25

26

if(action_id < 0){</pre>

println(info_table[1]);

28

}else{

29

perform_action(action_id);

30

31

}

32

33

command\_buffer\_pointer = 0x00;

memset(command_buffer, 0, sizeof(command_buffer));

35

}

36

return;

38

39

```

Listing XVI: The command parsing function

#### 4.3.2 Command parameters

Command paramters are interpreted as the string that follows the action and the space behind it. As can be seen in the case for ACTION\_USE in listing XVII the use item function is passed the command buffer<sup>L</sup> plus the length of the entered command plus one for the space. So the string starting at the passed address should match the start address of the parameter. If no parameter is supplied, the address should point to a character containing ASCII NUL, which marks the end of a string, bcause after comand parsing the string is overwritten with zeros as seen in listing XVI.

```

void perform_action(uint8_t action_id){

putchar_16550('\n', NULL);

2

switch(action_id){

3

default:

case ACTION_HELP:

println("You can:");

6

for(size_t i = 0; i < NUM_ACTIONS; i++){</pre>

println(" %s",action_table[i]);

break;

10

11

case ACTION_DESCRIBE:

12

describe_room(current_room, false);

13

break;

14

15

case ACTION_NORTH:

16

case ACTION_SOUTH:

case ACTION_WEST:

18

case ACTION_EAST:

move_direction(action_id -1);

break:

21

case ACTION_INVENTORY:

22

print_inventory();

23

break:

24

case ACTION_SEARCH:

25

print_room_item();

26

break;

27

case ACTION_TAKE:

28

consume_room_item(command_buffer+

strlen(action_table[ACTION_TAKE])+1);

30

break:

31

case ACTION_USE:

32

use_item(command_buffer+

33

strlen(action_table[ACTION_USE])+1);

34

```

Lwhich is an address in memory

```

break;

break;

println(info_table[3]);

return;

}

```

Listing XVII: The command execution routine

# 4.4 Gameplay

The game itself plays like a regular game with limitations set in direction. Playeras can search for items in each room and grab the found items as can be seen in figure xxix. The general gamplay is performed via altering the map data and the strings output to the user.

```

INIT

LONELY ROAD

You are on the dead end of a lonely road. You look right and left ofyou, but

you cannot remember why you are here... You are terrified.

MINIT

LONELY ROAD

You are on the dead end of a lonely road. You look right and left ofyou, but you cannot remember why you are here... You are terrified.

help

You can:

help

north

south

west

east

describe

use

inventory

search

take

Jhat are you going to do?

dearch

Invalid command!

search

You found a PISTOL

What are you going to do?

take pistol

You took the PISTOL

What are you going to do?

north

Moving towards north

S/N DIRT ROAD

You travel a bit towards the moon, you think that's the way to go. You find a bear in the middle of the road sleeping seemingly in peace.

What are you going to do?

use pistol

You can't use that!

What are you going to do?

use sausage

You can't use that!

What are you going to do?

search sauasage

You found a SAUSAGE

What are you going to do?

take sausage

You took the SAUSAGE

Jhat are you going to do?

use sausage

it ran away...

What are you going to do?

```

Figure xxix: A regular beginning of the game

# 4.5 Memory constraints

The AVR has 8kB of internal SRAM which are used for stack and heap [2]. During the build of the program an ELF file can be obtained which contains infromation on the programs structure and memory usage on boot. Strings and variables are contained within the .data section of the elf file, but loaded into the .bss section during boot[16]. This is done for integer variables, as well as for strings, which makes the use of strings limited not to the flash size but to the RAM size of the AVR. To save memory, sound tracks as well as the sine and noise table have been put into program space with the PROGMEM attribute as described by the avr-libc documentation[17]. In listing XII a read from program memory can be seen in the noise and sine modes.

# Part I

# A short introduction to VHDL

Designing a processor is a big task, and it's easiest to start very small. With software projects, this is usually in the form of a "Hello World" program - we will be designing a hardware equivalent of this.

## 5 Prerequisites

Other than a text editor, the following Free Software packages have to be installed:

```

ghdl [18] to analyze, compile, and simulate the design

gkwave [19] to view the simulation waveform files

yosys [20] to synthesize the design

ghdlsynth-beta [21] to synthesize the design

nextpnr-xilinx [22] to place and route the design

Project X-Ray [23] for FPGA layout data and bitstream tools

openFPGALoader [24] to load the bitstream onto the FPGA

```

#### 6 Creating a design

A simple starting design is an up/down counter. The following VHDL code describes the device:

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity counter is

6

port (

7

: in std_logic;

clk

reset : in std_logic;

enable : in std_logic;

reset

8

9

10

direction : in std_logic;

11

count_out : out std_logic_vector(7 downto 0)

12

```

Armin Brauns 50

```

13

);

14

end counter;

15

16

architecture behaviour of counter is

17

signal count : unsigned(7 downto 0) := (others => '0');

18

begin

19

proc: process(clk)

20

begin

21

if reset then

count <= (others => '0');

22

elsif rising_edge(clk) and enable = '1' then

23

if direction = '1' then

24

25

count <= count + 1;

26

else

27

count <= count - 1;</pre>

end if;

28

29

end if;

30

end process;

31

32

count_out <= std_logic_vector(count);</pre>

33

end behaviour;

```

counter.vhd

In order to test this design, a test bench has to be created:

```

library ieee;

use ieee.std_logic_1164.all;

3

use ieee.numeric_std.all;

entity counter_tb is

5

6

end counter_tb;

7

architecture test of counter_tb is

8

9

signal clk, reset, enable, direction : std_logic;

10

signal s_count_out : std_logic_vector(7 downto 0);

11

12

signal count_out : unsigned(7 downto 0);

13

begin

14

uut: entity work.counter

15

port map (

16

clk

=> clk,

=> reset.

17

reset

18

enable

=> enable,

19

direction => direction,

20

21

count_out => s_count_out

22

);

23

24

count_out <= unsigned(s_count_out);</pre>

25

26

simulate: process

27

begin

clk <= '0';

28

29

reset <= '1';

enable <= '0';

30

31

32

wait for 30 ns;

33

assert count_out = 0;

34

```

```

35

reset <= '0';

36

37

clk <= '0';

38

wait for 10 ns;

clk <= '1';

39

40

wait for 10 ns;

41

42

assert count_out = 0;

43

enable <= '1';

44

direction <= '0';</pre>

45

46

clk <= '0';

47

wait for 10 ns;

48

clk <= '1';

49

wait for 10 ns;

50

51

52

assert count_out = 255;

53

direction <= '1';</pre>

54

55

clk <= '0';

56

wait for 10 ns;

57

clk <= '1';

58

wait for 10 ns;

59

60

clk <= '0';

61

wait for 10 ns;

62

clk <= '1';

63

64

wait for 10 ns;

65

66

assert count_out = 1;

67

68

wait for 30 ns;

69

wait;

70

end process;

71

end test;

```

counter\_tb.vhd

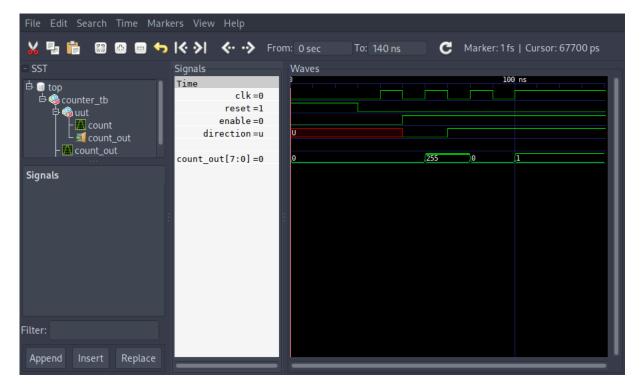

# 7 SIMULATING A DESIGN

Figure xxx: Screenshot of the resulting waveform in GTKWave

## 8 SYNTHESIZING A DESIGN

An additional Xilinx Design Constraints (XDC) file is required to assign the signals to pins on the FPGA:

```

set_property LOC D9

[get_ports clk]

set_property LOC C9

2

[get_ports reset]

set_property LOC A8

3

[get_ports enable]

4

set_property LOC C11 [get_ports direction]

6

set_property LOC F6

[get_ports count_out[0]]

7

set_property LOC J4

[get_ports count_out[1]]

set_property LOC J2

8

[get_ports count_out[2]]

set_property LOC H6

9

[get_ports count_out[3]]

set_property LOC H5

10

[get_ports count_out[4]]

set\_property\ LOC\ J5

11

[get_ports count_out[5]]

set_property LOC T9

12

[get_ports count_out[6]]

set_property LOC T10 [get_ports count_out[7]]

13

14

set_property IOSTANDARD LVCMOS33 [get_ports clk]

15

set_property IOSTANDARD LVCMOS33 [get_ports reset]

16

set_property IOSTANDARD LVCMOS33 [get_ports enable]

17

set_property IOSTANDARD LVCMOS33 [get_ports direction]

set_property IOSTANDARD LVCMOS33 [get_ports count_out[0]]

set_property IOSTANDARD LVCMOS33 [get_ports count_out[1]]

set_property IOSTANDARD LVCMOS33 [get_ports count_out[2]]

set_property IOSTANDARD LVCMOS33 [get_ports count_out[3]]

set_property IOSTANDARD LVCMOS33 [get_ports count_out[4]]

24

set_property IOSTANDARD LVCMOS33 [get_ports count_out[5]]

set_property IOSTANDARD LVCMOS33 [get_ports count_out[6]]

set_property IOSTANDARD LVCMOS33 [get_ports count_out[7]]

```

#### counter.xdc

```

# synthesize with yosys

yosys -m ghdl.so -p '

ghdl --std=08 counter.vhd -e counter;

synth_xilinx -flatten;

write_json counter.json'

# place and route the design with nextpnr

nextpnr-xilinx --chipdb xc7a35tcsg324-1.bin --xdc counter.xdc

-- ison counter. ison -- fasm counter. fasm

# convert the FPGA assembly to frames

fasm2frames.py --part xc7a35tcsg324-1 counter.fasm counter.

frames

# convert the frames to a bitstream

xc7frames2bit --part-name xc7a35tcsg324-1 --frm-file counter.

frames --output-file counter.bit

# upload the bitstream to the FPGA

openFPGALoader -b arty counter.bit

```

The current value of the counter is displayed in binary on the eight LEDs on the board. When switch 0 (enable) is in the high position, the counter can be advanced using button 0, with the direction set by switch 1. Button 1 resets the counter to zero.

# Part II

# Meta

#### 9 HISTORY

The project started out with the desire to build a CPU from scratch. Examples such as The NAND Game[25] and Ben Eater's Breadboard Computer series[26] served as inspirations and guidance during development.

At first, a design similar to Ben Eater's consisting solely of discrete integrated circuits was considered, but soon discarded in favor of an FPGA-based design. Designing the

Armin Brauns 54

logic alone was a difficult task, implementing it in discrete hardware would have pushed the project far over the allotted maximum development time.

RISC-V was chosen as the instruction set architecture for the processor. Its modular design with a very small base instruction set make it easy to implement a basic processor that is still fully compatible with existing software and toolchains.

As a starting point, a Terasic DE0 development board<sup>M</sup> containing an Altera Cyclone III<sup>N</sup> FPGA was borrowed from the school's inventory. It was used to implement a first version of the core.

The only method of synthesis for Altera devices is to use the proprietary Quartus IDE. However, the last version of Quartus to support the Cyclone III series of FPGAs (version 13.1) had already been out of date for several years at the start of the project. Because of this and the increasing resource demand of the developing core, an Arty A7-35T development board<sup>O</sup> with a Xilinx Artix-7<sup>P</sup> FPGA was ordered from Digilent.

The two FPGAs compare as follows:

|                | Altera EP3C16 | Xilinx XC7A35T |

|----------------|---------------|----------------|

| Logic Elements | 15000         | 33280          |

| Multipliers    | 56            | 90             |

| Block RAM (kb) | 504           | 1800           |

| PLLs           | 4             | 5              |

| Global clocks  | 20            | 32             |

The periphery on the development boards:

|          | Terasic DE0       | Digilent Arty A7-35T |

|----------|-------------------|----------------------|

| Switches | 10                | 4                    |

| Buttons  | 3                 | 4                    |

| LEDs     | 10 + 4x 7-segment | 4 + 3 RGB            |

| GPIOs    | 2x 36             | 4x PMOD + chipKIT    |

| Memory   | 8MB SDRAM         | 256MB DDR3L          |

| Others   | SD card, VGA      | Ethernet             |

|          |                   |                      |

While the Digilent board offers fewer IO options, the DDR3 memory can be interfaced using Free memory cores and allows for much larger programs to be loaded, possibly

Mhttps://www.terasic.com.tw/cgi-bin/page/archive.pl?No=364

Nhttps://www.intel.com/content/www/us/en/products/programmable/fpga/ cyclone-iii.html

Ohttps://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/

Phttps://www.xilinx.com/products/silicon-devices/fpga/artix-7.html

even a full operating system. The missing VGA port has been substituted by a HDMI-compatible DVI interface that is accessible through one of the high-speed PMOD connectors.

#### 10 Tooling

FPGA design is done using a Hardware Description Language (HDL). The two most well-known HDLs are Verilog and VHDL (VHSIC (Very high speed integrated circuit) HDL). As part of our studies at HTL, we exclusively worked with VHDL. For this reason, and because VHDL offers a better type system, it was chosen as the language of choice for the project.

### 10.1 Vendor Tools

The conventional way to work with FPGA designs is to use the FPGA vendor's development solution for simulation, synthesis and place-and-route. All of these tools are proprietary software specialized to a certain FPGA manufacturer, so a change of hardware also requires changing to a completely different software solution.

Vendor tools are usually free-of-charge for basic usage, but this also means there is no guaranteed support. During the development of this project, several bugs and missing features were found in vendor tools that required workarounds.

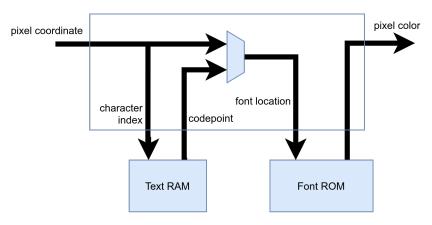

#### 10.2 Free Software Tools